【导读】电磁干扰EMI中电子设备产生的干扰信号是通过导线或公共电源线进行传输,互相产生干扰称为传导干扰。传导干扰给不少电子工程师带来困惑,如何解决传导干扰?这里,我们先着重讨论当寄生电容直接耦合到电源输入电线时会发生的情况。

1.只需几fF的杂散电容就会导致EMI扫描失败。从本质上讲,开关电源具有提供高dV/dt的节点。寄生电容与高dV/dt的混合会产生EMI问题。在寄生电容的另一端连接至电源输入端时,会有少量电流直接泵送至电源线。

2.查看电源中的寄生电容。我们都记得物理课上讲过,两个导体之间的电容与导体表面积成正比,与二者之间的距离成反比。查看电路中的每个节点, 并特别注意具有高dV/dt的节点。想想电路布局中该节点的表面积是多少,节点距离电路板输入线路有多远。开关MOSFET的漏极和缓冲电路是常见的罪魁祸首。

3.减小表面面积有技巧。试着尽量使用表面贴装封装。采用直立式TO-220封装的FET具有极大的漏极选项卡(drain tab)表面面积,可惜的是它通常碰巧是具有最高dV/dt的节点。尝试使用表面贴装DPAK或D2PAK FET取代。在DPAK选项卡下面的低层PCB上安放一个初级接地面板,就可良好遮蔽FET的底部,从而可显著减少寄生电容。

有时候表面面积需要用于散热。如果您必须使用带散热片的TO-220类FET,尝试将散热片连接至初级接地(而不是大地接地)。这样不仅有助于遮蔽FET,而且还有助于减少杂散电容。

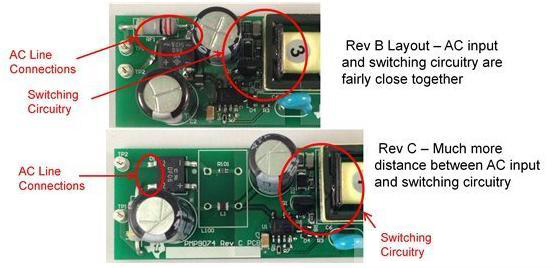

4.让开关节点与输入连接之间拉开距离。见图1中的设计实例,其中我忽视了这个简单原则。

图1.让输入布线与具有高 dV/dt 的节点靠得太近会增加传导 EMI。

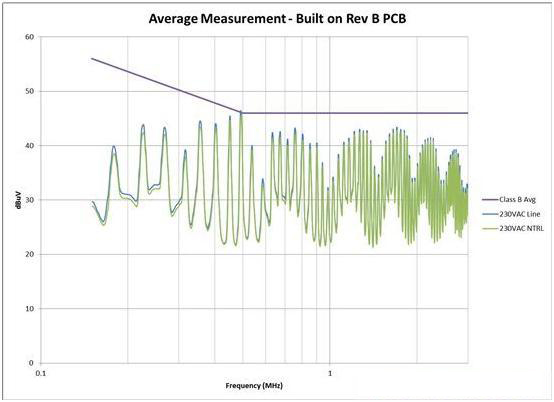

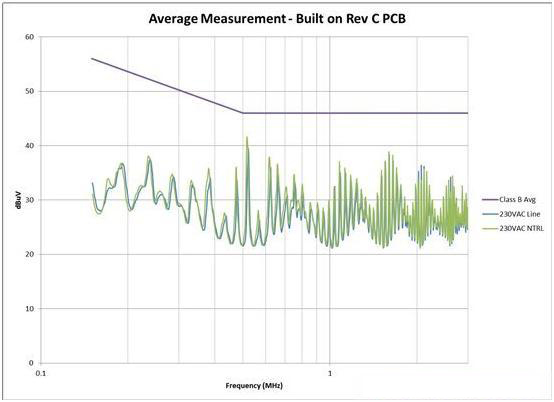

我通过简单调整电路板(无电路变化),将噪声降低了大约6dB。见图2和图3的测量结果。在有些情况下,接近高dV/dt进行输入线路布线甚至还可击坏共模线圈(CMC)。

图2.从电路板布局进行 EMI 扫描,其中 AC 输入与开关电路距离较近

图3.从电路板布局进行 EMI 扫描,其中 AC 输入与开关电路之间距离较大

你是否有过在显著加强输入滤波器后 EMI 改善效果很小甚至没有改善的这种遭遇?这很有可能是因为有一些来自某个高dV/dt节点的杂散电容直接耦合到输入线路,有效绕过了你的CMC。为了检测这种情况,可临时短路PCB上CMC的绕组,并将一个二级CMC与电路板的输入电线串联。如果有明显改善,你需要重新布局电路板,并格外注意输入连接的布局与布线。

现在,我们来看看共模EMI问题的最常见来源:电源变压器。

该问题由一次绕组和二次绕组间的寄生电容以及一次绕组的高dV/dt引起。这个绕组间的电容可起到充电泵的作用,导致杂散电流流到通常连接至接地的二次侧。这里有四个可最大限度减少该问题的常见技巧。

1.进行一次绕组,使最高dV/dt出现在外层上。电压电势会随每个匝数变化。例如在反激拓扑中,最大的电压摆幅出现在连接FET漏极的一端(见图1)。让“静音”层临近最近的二次层,可最大限度地降低在整个绕组间电容上出现的dV/dt。采用这种技术,应该明确外部绕组可能已成了有问题的噪声源,其可能会耦合至变压器附近的其它目标。外部绕组周围可能需要一个屏蔽绕组。

2.在一次绕组和二次绕组之间使用一个屏蔽绕组。插入一个一端连接至输入或输入返回端的单层绕组,可使杂散电流离开二次绕组并返回至源头。这种技术的代价是略微增加了变压器的设计复杂性,并增加了漏电感。

3.在一次接地到二次接地之间使用一个“Y电容器”。该电容器可为杂散电流提供一个回到一次接地的较低阻抗路径。电源中的这条本地路径可防止这些电流找到另外一条通过接地回到源头的路径。但是,对于能使用多大的电容,这里有一定安全限制。

4.添加一个共模线圈。有时候所提到的其它技术不足以将EMI降低到所需水平之下。添加一个共模线圈,不仅可增加共模阻抗,而且还对降低传导噪声非常有效。但这样会产生附加组件成本。在选择共模线圈时,要注意检查相 对于频率的阻抗曲线。在某种情况下,所有线圈都会因其自身的绕组间电容问题而转变成电容性。

转载自电子元件技术网